W miarę upływu lat obserwuję spadek zainteresowania w budowaniu własnych urządzeń odbiorczo-nadawczych. O ile budowa urządzeń QRO jest dość kosztowna, to pewne zdziwienie budzi spadek zainteresowania w konstruowaniu urządzeń QRP; nawet tych, których kity są powszechnie dostępne. Ma to przełożenie na wyniki tegorocznego (2024) SP QRP Contestu, w którym zaledwie 25,6 % uczestników posługiwało się urządzeniami home made [1].

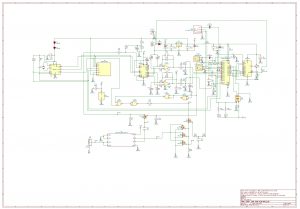

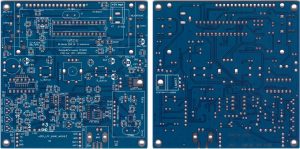

Projektowi uSDX [2] przyglądałem się prawie od chwili, gdy pojawił się on w Internecie. Jednak do podjęcia praktycznych działań skłoniła mnie dostępność płytek drukowanych do wersji (1.02) opisanej przez Barbarosa WB2CBA [3] i udostępnionych przez Andrzeja SP8NTP. Schemat oryginalnie opublikowanego [3] układu pokazano na Rys. 1, a fotografie płytki drukowanej na Fot. 1.

Należy zauważyć, że płytka Andrzeja różni się od oryginału [3] tym, iż oprócz standardowych footprintów wprowadzono na niej również alternatywne footprinty dla danych typów układów scalonych. Ponadto znajduje się na niej zwora (R29 – SMD), której rozłączenie umożliwia programowanie procesora ATMega328 za pomocą złącza ISP. Ponadto na płytce umieszczono sześciopinowe złącze ISP zgodne ze standardem ustanowionym przez firmę Atmel. Stanowi to poważne ułatwienie w programowaniu procesora (np. programatorem ArduinoISP) bowiem łącze ISP (ICSP) można wykorzystywać niezależnie od częstotliwości zegara procesora. Uwaga – na schemacie z Rys. 1 oba wymienione elementy nie są narysowane. Takie usprawnienie zwalnia konstruktora z konieczności wgrywania do procesora zmodyfikowanego BootLoader’a. Montując procesor w podstawce można go programować zewnętrznym programatorem co uważam za znacznie wygodniejsze rozwiązanie. Należy podkreślić, że układ uSDX będzie pracował poprawnie wówczas gdy w miejsce zwory (R29) będzie wlutowany opornik 0R (SMD).

Montaż

Przed rozpoczęciem montowania elementów warto sprawdzić omomierzem połączenia pomiędzy wszystkimi polami lutowniczymi (padami). Szczególnie dotyczy to tych ścieżek, które posiadają przelotki. Cóż, jakość obwodów drukowanych zamawianych „po taniości” u różnych producentów może pozostawiać wiele do życzenia. Niestety część płytek Andrzeja „cierpiała” na tą przypadłość.

Po uruchomieniu układu sprawdziłem poziom szumu jaki był przenoszony wzdłuż magistral zasilania i stwierdziłem, że koniecznym jest zwiększenie pojemności C1, C4, C5 do wartości 470 µF. Przy czym kondensator C1 powinien być dostosowany do pracy z napięciem co najmniej 16 V. Chociaż zwiększenie tych pojemności spowodowało spadek poziomu szumów zasilania o połowę zarówno dla magistral 12 V jak też i 5 V to decyzję o tej zamianie pozostawiam Czytelnikowi. Wszystkie wyprowadzenia tranzystora Q5 powinny być ze sobą zwarte. Podczas montażu należy pominąć rezystor R28. Celem zastosowania obu tych elementów była chęć zwiększenia prądu ładowania pojemności wejściowej tranzystorów Q2 – Q4. Niestety za wysterowanie stopnia PA odpowiedzialny jest nie tylko prąd ładowania, ale i rozładowania pojemności bramek. Tego jednak układ z Rys. 1 nie jest w stanie zapewnić i stąd wzięła się moja uwaga upubliczniona w Internecie [4], jak dotąd bez odpowiedzi.

Podczas montażu można pominąć elementy wchodzące w skład VFO zbudowanego na układzie SI5351A – lewy układ na Fot. 2. W takim przypadku można zastosować przerobiony moduł generatora – lewe zdjęcie Fot. 3. Przeróbki należy wykonać zgodnie z opisem pokazanym na stronach HF5L i upublicznionym przez Mirka SP5GNI [5]. Można też wykonać własny moduł na małej płytce drukowanej „wtykanej” z złącze U6 – vide prawe zdjęcie Fot.3. Chociaż w układzie VFO uSDX można stosować rezonatory kwarcowe 25 MHz lub 27 MHz to wolałem stosować te drugie, bowiem ich częstotliwość podstawowa lub pierwsza harmoniczna są oddalone od częstotliwości pasma 12 m i 6 m.

Koniecznym jest jeszcze omówienie detektora kwadraturowego zbudowanego na układzie FST3253 (a właściwie na układzie SN74FST3253) jak to pokazano na Rys. 1. Kłopot tylko w tym, że wszystkie zakupione przeze mnie (na azjatyckim portalu) układy FST3253 nie działały. W ich miejsce zastosowałem układy SN74CBT3253D, ale zakupione już na innym portalu. Niestety oba typy układów różnią się działaniem wyprowadzeń Enable (OE), a mianowicie w FST3253 każde z dwóch wyprowadzeń OE, stanem 0 „włącza” jedną z dwóch czterobitowych magistral „przełączników” (BUS). Natomiast w przypadku układu SN74CBT3253D, stan 0 na obu wyprowadzeniach OE, jest niezbędny do włączenia wszystkich ośmiu „przełączników”. Skoro w przypadku zastosowanego detektora używane są jedynie cztery „przełączniki” to pozostałe cztery (nawet przełączane sygnałem VFO) nie wpływają na działanie układu. Wyzerowanie obu wyprowadzeń OE we wlutowanym układzie SN74CBT3253D wymaga odgięcia wyprowadzenia 15 do góry i połączenia go z masą występującą na wyprowadzeniu 1. „Drucianą zworę” widać na wszystkich zdjęciach Fot. 2 i 3.

Przygotowanie „wsadu” do procesora

Do przygotowania „wsadu” do procesora ATMega328 wykorzystałem wersję 1.02w pobraną ze strony [2]. Po jej uruchomieniu w programie Arduino IDE [6] koniecznym jest wprowadzenie poprawek w kilku liniach:

– w linii

#define F_XTAL 27005000 // 27MHz SI5351 crystal

należy wpisać (decymalnie) częstotliwość pracy generatora pracującego w układzie SI5351A. Poprawkę będzie można nanieść również po uruchomieniu transceivera uSDX,

– w linii

#define SWAP_ROTARY 1 // Swap rotary direction (enable for WB2CBA-uSDX)

należy usunąć znak komentarza znajdujący się na początku linii – //,

– w linii

#define SIDETONE 11 //PB1 (pin 15)

należy zmienić parametr liczbowy z 9 na 11,

– w linii

#define SIG_OUT 9 //PB3 (pin 17)

należy zmienić parametr liczbowy z 11 na 9.

Po wprowadzeniu powyższych poprawek należy skompilować program, a następnie „wgrać” do procesora. Zainteresowani mogą, przed kompilacją, zmodyfikować BootLoader tak aby współpracował on z zegarem procesora o częstotliwości 20 MHz. Wobec tego co napisałem powyżej tym zagadnieniem nie będę zajmował się tutaj traktując je jako zbędne.

Uruchomienie transceivera

Po dołączeniu wyświetlacza LCD do płytki i po włączeniu zasilania (12 V) najczęściej uzyskamy informacje pokazane na Fot. 4. Aby otrzymać odpowiednio ostry obraz wystarczy dobrać odpowiednią pozycję potencjometru montażowego RV1. Taki obraz świadczy o prawidłowej współpracy mikrokontrolera z urządzeniami peryferyjnymi i tylko o tym.

Na lewej fotografii Fot. 5 pokazałem reakcję uSDXa na brak wmontowanego VFO. Jak widać ekran jest całkowicie pusty, ale jeśli zmienilibyśmy w procesorze ustawienia Fuse Bits High na 0xD7 to na ekranie pojawiłby się komunikat: !!V3.3=1V. Natomiast stosując oprogramowanie do wersji z automatycznie przełączanymi pasmami, w przypadku niepodłączonego demultipleksera TCA9555, pojawiłby się również komunikat: !!BER_I2C=4989. Jak widać to oprogramowanie uSDX posiada automatyczną detekcję błędów współpracy procesora z zewnętrznymi urządzeniami. Można o tym przekonać się również zwierając do masy gniazdo klucza telegraficznego i włączając zasilanie uSDXa – vide komunikat na ekranie LCD na prawym zdjęciu Fot. 5.

Poszukiwanie ewentualnej usterki należy rozpocząć od resetu procesora. Można go wykonać „wciskając” przycisk enkodera i włączając napięcie zasilania uSDXa. Jeśli to nie da pozytywnego efektu, należy sprawdzić ustawienia Fuse Bits. Powinny one wynosić (w wersji 1.02w): Extended 0xFD, High 0xDE, Low 0xFF. Sprawdzenia można dokonać zewnętrznym programatorem przez złącze ISP (ICSP), również przez to dodane do układu i umieszczone na płytce Andrzeja SP8NTP.

Dopiero po sprawdzeniu poprawności wprowadzonego software’u i konfiguracji procesora (Fuse Bits) należy zająć się sprawdzaniem ewentualnych usterek w hardware’rze. Sprawdzić należy oscyloskopem sygnał zegara procesora (wyprowadzenie 10) a także wyjście głośnikowe z procesora (wyprowadzenie 15). Na tym wyjściu powinien być obecny sygnał o częstotliwości około 70 kHz i amplitudzie bliskiej napięciu zasilania (5 V). W kolejnym kroku, na gnieździe U6 wyprowadzenia 6 i 7, należy sprawdzić oscyloskopem obecność sygnału VFO podczas odbioru i na wyprowadzeniu 5 podczas nadawania. Warto również sprawdzić zgodność generowanych częstotliwości z częstotliwością pokazywaną na wyświetlaczu LCD i w razie rozbieżności dokonać korekty we wgranym do procesora „wsadzie” – vide linia:

#define F_XTAL 27005000 // 27MHz SI5351 crystal.

Ze względu na jakość kupowanych układów scalonych warto napisać coś o najprostszym sprawdzaniu detektora kwadraturowego. Pomiędzy wejście odbiornika RD i masę należy doprowadzić sygnał o danej częstotliwości w zakresie od 1 MHz do 30 MHz (1 mW na 50 Ω – np. z nanoVNA ) i VFO nastroić na częstotliwość o mniej więcej 1 kHz różną od tej doprowadzonej. Następnie na wyprowadzeniach 10, 11, 12 i 13, sprawdzić obecność sygnału m.cz. Częstotliwość owego sygnału m.cz., na wszystkich podanych wyprowadzeniach, powinna być równa różnicy częstotliwości obu sygnałów doprowadzonych do detektora, jego obwiednia powinna mieć kształt sinusoidy, a amplituda powinna znaleźć się w zakresie około 100÷150 mV. Jeśli spełnione są te warunki to można uznać, że detektor działa prawidłowo. Najlepiej byłoby gdyby amplituda sygnału m.cz. była taka sama na każdym z wyprowadzeń, aczkolwiek podczas prób z układami SN74CBT3253 nie znalazłem ani jednego egzemplarza spełniającego to wymaganie. Cóż, najwidoczniej kanały łączące wejście detektora z wyjściami miały różne oporności, jednak nie stanowi to przeszkody dla przetworników ADC wbudowanych w mikroprocesor i ich prawidłowej pracy. Należy podkreślić, że brak sygnału na którymkolwiek z podanych wyprowadzeń dyskwalifikuje poprawną pracę detektora.

W trakcie „zabawy” z detektorami sprawdziłem również detektor wykorzystujący układ 74HC4053 [5]. Obwiednie sygnałów pojawiających się na wyjściach tego detektora (o numerach 1, 2, 3 i 5) miały trójkątny kształt, zamiast sinusoidalnego. Zasadniczo nie powoduje to wadliwej pracy detektora, ale ma wpływ na poziom szumów odbiornika. Wobec poziomu zakłóceń występujących na niższych pasmach nie ma to większego znaczenia, jednak może mieć znaczenie na „cichszych”, wyższych pasmach.

W swoim artykule [5], Mirek SP5GNI zwrócił bardzo istotną uwagę dotyczącą dzielników zbudowanych na rezystorach R10, R11 i R12, R13. Otóż różnica napięć pomiędzy punktami, do których przyłączone są kondensatory C12 i C13 powinna być mniejsza niż 5 mV. Warunek ten wymusza dobieranie rezystorów wchodzących w skład tych dzielników. Pewnym problemem jest to, że napięcie AREF (wyprowadzenie 21 procesora) zmienia się dwustanowo w trakcie pracy odbiornika (2,56 i 5 V). Wyższe napięcie występuje gdy do wejścia odbiornika jest dostarczony silny sygnał w.cz. „generujący” silny sygnał m.cz. Zatem owe 5 mV należałoby sprawdzać wtedy gdy dołączony jest do wejścia odbiornika generator. Jednak dokładne dobranie rezystorów R10, R11 i R12, R13 (z dokładnością równą lub lepszą od 1%) zwalnia konstruktora z konieczności wykonania takiego pomiaru. Warto zauważyć, że opisany pomiar można przeprowadzić, po wyjęciu z podstawki procesora, dołączając do jego wyprowadzenia 21 napięcie +5 V.

Oprócz standardowo używanego wzmacniacza operacyjnego LM4562 sprawdziłem działanie „niskoszumnego” układu LT6231. Stwierdziłem, że przy zwartym do masy wejściu odbiornika, rzeczywiście ten drugi układ generuje mniejszy szum. Jednak różnica jest na poziomie połowy jednostki S, co przy szumach pasma jest wielkością znikomą. Natomiast różnica w cenie pomiędzy oboma układami jest znacząca.

Filtry pasmowe

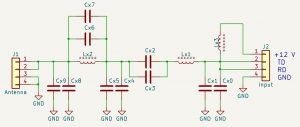

Filtry pasmowe jakie zaproponował Barbaros WB2CBA na swojej stronie [3] są filtrami dolnoprzepustowymi typu m. Jak sprawdziłem to filtry te mają „przyzwoite” tłumienie powyżej pasma przepuszczania, jednakże mają również spore tłumienie w paśmie przepuszczania. Skutkiem tego sprawność wzmacniacza mocy i filtru pasmowego nawet na niższych pasmach wynosi około 40%. Z tego powodu w budowanych transceiverach uSDX zastosowałem filtry preferowane przez Mirka SP5GNI [5], Manuela DL2MAN [7, 8] i później Barbarosa WB2CBA [3] o schemacie pokazanym na Rys. 2.

W zasadzie pokazany filtr jest dwuobwodowym filtrem pasmowym; pierwszy od prawej jest obwodem pasmowo przepustowym dla pożądanego pasma, a drugi jest obwodem pasmowo zaporowym o największym tłumieniu „ustawionym” na częstotliwości wyższej od częstotliwości przepuszczanego pasma. Charakterystyki przykładowych filtrów na pasma 80 m (po lewej) 60 m (po prawej) pokazano na Fot. 6.

W ogólnym przypadku to układ PA z filtrami pasmowymi można stroić na „maksimum mocy wyjściowej”, na „minimum harmonicznych”, na „maksimum sprawności” itd. Pierwsze podejście ma tą wadę, że sygnał wyjściowy może zawierać dowolną ilość „brudu”, w drugim umożliwia najskuteczniejsze ograniczenie zakłóceń, ale wymaga zastosowania analizatora widma. Niestety takiego urządzenia nie posiadam, zatem pozostało mi tylko trzecie podejście.

Największe tłumienie filtru pasmowego powinno występować co najwyżej na częstotliwości pierwszej harmonicznej pasma przepustowego. Natomiast najmniejsze tłumienie powinno występować w paśmie przepuszczania. Oba pokazane filtry (Fot. 6) spełniają te warunki – vide jasno niebieska linia. Patrząc z drugiej strony to filtr powinien charakteryzować się wartością SWR jak najbliższą jedności. Tego warunku nie spełniają oba pokazane filtry. Należy jednak pamiętać o tym, że nanoVNA wymaga dopasowania wejścia i wyjścia układu do 50 Ω. O ile wyjście filtru, na podstawie obliczeń, spełnia ten warunek to jego wejście powinno być dopasowane do bliżej nieznanej impedancji wyjściowej tranzystorów PA. Niestety danej tej nie udało mi się znaleźć w dostępnych danych technicznych tranzystorów zatem pozostało mi jedynie manualne dobieranie pojemności Cx0 i Cx1 (przede wszystkim), a następnie pozostałych elementów co najmniej wchodzących w skład pierwszego „oczka” filtru. Najprawdopodobniej z powodu niedopasowania wyjścia nanoVNA do wejścia filtru pasmowego występuje przesunięcie częstotliwości minimum tłumienia filtru i minimum współczynnika SWR (żółta linia) widoczne na Fot. 6, a także zaskakujące zachowanie wykresu Schmidta (zielona linia). Strojenia filtrów pasmowych nie ułatwiają zmiany parametrów tranzystorów PA występujących podczas ich pracy – vide zmiana ich temperatury. Zatem należy spodziewać się, że wszystkie publikowane wartości cewek i kondensatorów stanowią pewne optimum.

Aby zmniejszyć liczbę dobieranych, niezależnych parametrów, a przy okazji uzyskać dane do urządzenia wielopasmowego z przełączanymi filtrami pasmowymi, przyjąłem niezmienność indukcyjności Lx3 znajdującej się w drenie tranzystorów PA. Owa indukcyjność, na każdym paśmie, stanowi 23 zwoje drutu DNE 0,4 nawinięte na rdzeniu ferrytowym FT37-43. Przy czym 23 zwoje oznaczają liczbę „przewleczeń” drutu przez wewnętrzny otwór rdzenia. Ten sposób liczenia zwojów zastosowano w przypadku wszystkich cewek podanych w Tabeli 1 zawierającej dane wszystkich zbudowanych i sprawdzonych filtrów pasmowych.

Tabela 1. Wartości pojemności i indukcyjności w filtrach pasmowych dla wszystkich pasm.

|

pasmo |

Cx0+Cx1 [pF] | Cx2+Cx3 [pF] | Cx4+Cx5 [pF] | Cx6+Cx7 [pF] | Cx8+Cx9 [pF] | Lx1 zwoje/typ rdzenia | Lx2 zwoje/typ rdzenia |

| 160 m | 1306 | 3824 | 3813 | 1176 | 3817 | 33zw/T37-2 | 21zw/T37-2 |

| 80 m | 680 | 1860 | 1800 | 620 | 1800 | 20zw/T37-2 | 14zw/T37-2 |

| 60 m | 430 | 1240 | 1200 | 390 | 1200 | 17zw/T37-2 | 12zw/T37-2 |

| 40 m | 307 | 931 | 1040 | 305 | 1040 | 14zw/T37-2 | 10zw/T37-2 |

| 30 m | 201 | 660 | 645 | 210 | 645 | 12zw/T37-2 | 8zw/T37-2 |

| 20 m | 126 | 472 | 467 | 156 | 463 | 10zw/T37-2 | 7zw/T37-2 |

| 20 m | 126 | 455 | 455 | 156 | 455 | 12zw/T37-6 | 8zw/T37-6 |

| 17 m | 91 | 360 | 360 | 120 | 360 | 11zw/T37-6 | 6zw/T37-6 |

| 15 m | 68 | 315 | 300 | 100 | 300 | 9zw/T37-6 | 6zw/T37-6 |

| 12 m | 47 | 264 | 273 | 83 | 272 | 8zw/T37-6 | 6zw/T37-6 |

| 11 m | 39 | 241 | 251 | 76 | 250 | 9zw/T37-6 | 6zw/T37-6 |

| 10 m | 39 | 240 | 240 | 75 | 240 | 9zw/T37-6 | 5zw/T37-6 |

| 6 m | 0 | 141,1 | 146,8 | 37,1 | 145,9 | 8zw/T37-10 | 6zw/T37-10 |

Należy tutaj zaznaczyć, że filtr pasmowy na 80 m, pokazany w Tabeli 1, został zestrojony na górną część pasma (SSB). Jeśli miałby być zestrojony na dolną część pasma to liczbę zwojów cewki Lx1 należy zwiększyć o jeden. Wszystkie z indukcyjności podanych w Tabeli 1 były nawijane drutem DNE 0,4, a pojemności dobierano z dokładnością nie gorszą niż 1%.

Wyniki doświadczeń

Na płytce Andrzeja SP8NTP należy „drucianą” zworą połączyć zasilanie PA oznaczone jako +12 V z punktem +12 V znajdującym się za diodą D1 lub z dodatnim wyprowadzeniem gniazda zasilania J2. Rozdzielenie na płytce zasilania drenów tranzystorów PA od reszty układu znacząco ułatwia mierzenie mocy do nich doprowadzonej poprzez pomiar natężenia prądu do nich dopływającego.

Dzięki takiemu rozwiązaniu można zasilać część odbiorczą transceivera napięciem 12 V, a doświadczenia z filtrami pasmowymi można przeprowadzić przy napięciu zasilania PA równym 12 V, 13,8 V i 14,4 V (połączone szeregowo cztery akumulatory litowo-jonowe np. 18650) chociażby tylko dla środkowej częstotliwości pasma. Jako obciążenie stosowano bezindukcyjny rezystor 50 Ω, a pomiarów napięć na nim występujących dokonywano za pomocą oscyloskopu. Uzyskane wyniki podano w Tabeli 2.

Tabela 2. Wyniki pomiarów obrazujących współpracę PA z filtrami pasmowymi.

| pasmo | Moc output W (12 V) | Sprawność % | Moc output W (13,8 V) | Moc output W (14,4 V) |

| 160 m | 2,1 ÷ 4,0 | 50,3 ÷72,1 | 3,3 ÷ 4,0 | 3,3 ÷ 4,2 |

| 80 m | 3,3 ÷ 4,65 | 50,1 ÷ 63,8 | 4,9 | 5,1 |

| 60 m | 2,8 ÷ 2,9 | 53,8 ÷ 58,0 | 3, 5 ÷ 3,6 | 3,6 ÷ 4,0 |

| 40 m | 2,4 ÷ 3,1 | 47,1 ÷ 51,1 | 3,4 ÷ 3,8 | 3,4 ÷ 4,0 |

| 30 m | 2,6 ÷ 3,1 | 44,7 ÷ 53,0 | 3,1 ÷ 3,8 | 3,3 ÷ 4,0 |

| 20 m | 2,0 ÷ 2,5 | 36,6 ÷ 42,1 | 2,6 ÷ 2,7 | 2,7 ÷ 2,9 |

| 17 m | 1,4 ÷ 1,6 | 26,8 ÷ 30,0 | 1,8 | 1,9 ÷ 2,0 |

| 15 m | 1,3 ÷ 1,6 | 23,2 ÷ 26,0 | 1,7 | 1,8 |

| 12 m | 1,3 ÷ 1,6 | 23,6 ÷ 30,9 | 1,8 | 1,8 ÷ 2,0 |

| 11 m | 1,0 ÷ 1,2 | 22,8 ÷ 26,3 | 1,4 ÷ 1,5 | 1,4 ÷ 1,6 |

| 10 m | 0,7 ÷ 1,1 | 25,0 ÷ 35,2 | 1,2 | 1,2 |

| 6 m | 0,11 ÷ 0,16 | 3,0 ÷ 3,9 | 0,13 ÷ 0,14 | 0,13 ÷ 0,15 |

Wyniki pokazane w Tabeli 2 jednoznacznie wskazują na to, że układ PA i filtru pasmowego pogarsza się wraz ze wzrostem częstotliwości pasma. Dotyczy to zarówno oddawanej mocy (output) jak również sprawności takiego układu. Ma to związek z „dokładnością” nawijania uzwojeń (do 0, 5 zwoja) na co wskazują wyniki na wyższych pasmach i związanego z tym dopasowania tranzystorów PA i filtru pasmowego. Również ma na to wpływ rosnąca, wraz z częstotliwością, stratność rdzeni ferrytowych. Mogłem to zaobserwować badając tłumienie filtrów (w paśmie przepuszczania) wraz ze zwiększaniem częstotliwości ich pracy. Radykalne załamanie się oddawanej mocy i sprawności badanego układu dla pasma 6 m ma zapewne związek z czasami otwarcia i zamknięcia tranzystorów. Ta dana katalogowa wynosi maksimum 10 ns co limituje częstotliwość pracy PA. Dodatkowo, połączenie równoległe trzech tranzystorów BS170 powoduje, że układ ten pracuje tak jak na to pozwala najgorszy egzemplarz. Patrząc od strony sterowania PA to łatwo można zauważyć, że pojemność bramki jest „przeładowywana” za pomocą układu 74ACT00 o ograniczonej wydajności prądowej. Zatem im krótszy jest prostokątny impuls wejściowy tym do niższego napięcia owa pojemność może naładować się. To zaś odpowiada za stosunkowo wysoką oporność otwarcia źródło-dren. Owszem, po kilkudziesięciu impulsach ładowania i rozładowania napięcie na bramce rośnie do poziomu wystarczającego na otwarcie tego kanału, czyli przez źródło-dren zaczyna przepływać względnie duży prąd, ale wahania tego prądu są stosunkowo niewielkie i wytwarzana moc w.cz. spada. To zaś powoduje spadek sprawności (zmiennoprądowej) układu PA wraz ze wzrostem częstotliwości jego pracy.

Kończąc budowę transceivera uSDX wypadałoby jego płytkę umieścić w jakiejś obudowie. Do wyboru są obudowy oferowane komercyjnie [9]. Jednak wobec systematycznego rozwoju projektu znacznie korzystniej jest przygotować jedynie „płytę czołową” i „płytę tylną” urządzenia [10]. Ja również zastosowałem to rozwiązanie – vide Fot. 8.

Transceiver uSDX jest dość prostym urządzeniem nadawczo-odbiorczym, chociaż jego uruchomienie może sprawiać pewne trudności konstruktorom przyzwyczajonym do budowy urządzeń wykorzystujących filtry kwarcowe. Zastosowanie detektora kwadraturowego, rzadko wykorzystywanego w urządzeniach krótkofalowych, a także cyfrowej obróbki sygnałów (odbieranego i nadawanego) wymaga zapoznania się z kilkoma nowymi zagadnieniami. Tym niemniej istotnymi ułatwieniami są: zastosowanie prostego układu elektronicznego i łatwego do opanowania systemu mikroprocesorowego (Arduino). Dla osób dopiero zapoznających się z oboma zagadnieniami nie bez znaczenia jest również i to, że finansowe nakłady na samo urządzenie są stosunkowo niewielkie.

Wyniki pokazane w artykule wskazują na sporą zależność działania nadajnika uSDX od zastosowanych tranzystorów PA i rdzeni użytych w filtrach pasmowych. Zatem wykonanie transceivera uSDX będzie związane z poświęceniem mu pewnego czasu. Jednakże modułowa budowa filtrów pasmowych pozwala na jego użytkowanie już od chwili zmontowania pierwszego filtru pasmowego. Jest to korzystne szczególnie dla tych koleżanek i kolegów, którzy mogą poświęcić na konstrukcje trochę czasu, ale co pewien czas.

Na jednym ze zbudowanych transceiverów uSDX przeprowadziłem kilkadziesiąt łączności w paśmie 80 m emisją SSB. Wybrałem tą emisję bowiem najczęściej konstruktorzy tego urządzenia spotykają się z utyskiwaniami respondentów co do marnej jakości sygnału. Rozmowy na paśmie i otrzymywane raporty wcale nie potwierdzają takiego przekonania. Transceiver bez problemu „daje radę” aby prowadzić „pogaduchy” na tym paśmie.

Wziąłem też udział w tegorocznych zawodach SP QRP. Nie jestem asem sztuki operatorskiej, ale uważam, że i w tego rodzaju wyzwaniu urządzenie sprawdziło się. Owszem przed zawodami trzeba dość dokładnie zapoznać się z Menu transceivera, jednak o tym może napiszą inni gdy nabiorą mistrzowskiej biegłości.

Oprogramowanie uSDX’a jest oprogramowaniem wielowariantowym. Oznacza to, że jego fragmenty można włączać i wyłączać (przez dodanie lub usunięcie znaku komentarza – //) w nagłówkowej części programu. Tego w tym artykule nie pokazałem bowiem dotyczy on tylko uruchomieniu urządzenia. Aczkolwiek, po jego uruchomieniu można wyłączyć „śledzenie błędów” odciążając pracę procesora; w tym celu można również wyłączyć szereg „wodotrysków” (np. dekodowanie telegrafii, interfejs CAT itp.). Można również dokonać korekty odbieranego i nadawanego sygnału np. poprawiając sprawność nadajnika. Patrząc od strony hardware’u to można połączyć równolegle bramki C i D układu U7 po to aby zwiększyć prąd ładowania bramek tranzystorów Q2÷Q4 podczas nadawania. Takie rozwiązanie mogłoby zwiększyć moc transceivera na wszystkich pasmach.

Podczas użytkowania uSDX’a zauważyłem pewną cechę, która może być uważana za wadę. Mianowicie urządzenie to dość chimerycznie współpracuje z mikrofonogłośnikiem, słuchawkami itp. Otóż niektóre egzemplarze wzbudzają się gdy ustawia się maksymalny poziom głośności. Jak sprawdziłem to nie jest to spowodowane sprzężeniem „głośnika” z wejściem odbiornika lub wejściem układu wzmacniacza m.cz. Problem ten jest spowodowany sprzężeniem pomiędzy wyjściem głośnikowym i przetwornikami ADC wewnątrz struktury mikrokontrolera. Zatem jakość użytego procesora będzie miała wpływ na „głośność” urządzenia. Należy jednak zaznaczyć, że dla mniejszego poziomu głośności odbiornik zadowalająco współpracuje ze słuchawkami lub wzmacniaczem m.cz. w komputerze.

Jacek Michalski, SP5IMO & ex WX3V

Literatura

- https://logsp.pzk.org.pl/?page=contest&id=1973

- https://github.com/threeme3/usdx

- https://antrak.org.tr/blog/usdx-an-arduino-based-sdr-all-mode-hf-transceiver-pcb-iteration-v1-02/

- http://sp-hm.pl/thread-3992-page-29.html?highlight=uSDX

- https://hf5l.pl/radio-definiowane-programowo-z-adruino-nano/

- https://www.arduino.cc/en/software

- https://dl2man.de/wp-content/uploads/2021/03/uSDX_RF-Board-MULTIBAND-for-Rev2-Sandwich.pdf

- https://dl2man.de/wp-content/uploads/2021/08/uSDX_Multiband_Board_Rev3.1.pdf

- https://www.printables.com/model/459769-wb2cba-usdx-case-and-lpf-box

- https://antrak.org.tr/blog/usdx-sdr-ssb-sota-transceiver-battery-pack/

Skomentuj